트윈 빅스 플래시는 기존의 원형 차지 트랩 셀에 비해 셀 크기가 훨씬 작으면서도 월등한 프로그램 슬로프와 더 큰 사이즈의 프로그램/삭제 윈도를 갖고 있다. 이들 특성으로 인해 새로운 셀 디자인은 적은 수의 스태킹 레이어에도 불구하고 메모리 밀도가 훨씬 높은 셀당 4비트를 초과하는 유망한 후보가 되고 있다. 이 기술은 지난 12월 11일 샌프란시스코에서 열린 IEEE 국제반도체소자학회에서 발표되었다.

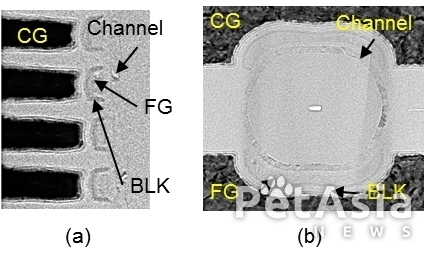

3D 플래시 메모리 기술은 셀 스택 레이어 수를 늘리고 다중 레이어 스택 증착을 실행하는 동시에 높은 가로세로 비율의 식각 기술을 도입함으로써 비트당 비용을 낮추면서도 비트 밀도를 높이는 성과를 거두었다. 최근 몇 년 사이에 셀 레이어 수가 100개를 넘어섬에 따라 식각 프로필 컨트롤과 사이즈 일률성, 생산성 사이의 상충관계를 관리하는 일이 점차 더 어려워지고 있다. 이러한 문제를 극복하는 방안으로서 키옥시아는 기존의 원형 셀과 대비하여 셀 사이즈를 줄이기 위해 기존 원형 셀의 게이트 전극을 둘로 나눠서 새로운 반원형 셀 디자인을 개발해냈으며 이로써 적은 수의 셀 레이어에도 불구하고 더 높은 메모리 밀도를 구현할 수 있었다.

원형 컨트롤 게이트는 그 곡선 효과로 인해 평면 게이트에 비해 포화 문제가 덜 심각하며 이에 따라 더 큰 사이즈의 프로그램 윈도를 제공한다. 이를 통해 터널 유전체를 통한 캐리어 주입이 더 쉬워지고 블록 유전체로의 전자 누출이 줄어들 수 있다. 이와 같은 스플릿 게이트 셀 디자인에서 원형 컨트롤 게이트는 프로그램/삭제 다이나믹에서 높은 향상 효과를 내기 위해 두 개의 반원형 게이트로 대칭형으로 분리된다. 그림 1에서 나타난 것과 같이 높은 k BLK 유전체와 함께 높은 차지 트랩 효율을 위해 전도성 축적 레이어가 채택되어 프로그램 윈도를 얻고 FG로부터 전자 누출을 낮추기 위해 높은 커플링 비율을 성취할 수 있다. 또 그럼으로써 포화 문제를 해소할 수도 있다.

그림 2에서 실험적 프로그램/삭제 특성을 보면 높은 k 기반 BLK와 결합된 반원형 FG 셀이 프로그램 슬로프와 프로그램/삭제 윈도 측면에서 대규모 원형 CT 셀에 비해 훨씬 월등한 성과를 나타냄을 알 수 있다. 월등한 프로그램/삭제 특성을 갖고 있는 반원형 FG 셀은 셀 사이즈가 작은 경우에도 상대적으로 조밀한 QLT Vt 분배 패턴을 얻을 수 있다. 이에 더해서 낮은 트랩 Si 채널의 통합은 그림 3에서 볼 수 있듯이 예를 들어 펜타 레벨 셀 같이 셀당 4비트 이상을 구현할 수 있게 한다. 이러한 결과는 반원형 FG 셀이 높은 비트 밀도를 가능하게 하는데 상당히 유망한 옵션이 됨을 입증한다.

장래에 플래시 메모리 분야 이노베이션에 초점을 맞춘 키옥시아의 연구개발 노력은 계속해서 트윈 빅스 플래시 개발과 이와 관련된 실용적 어플리케이션에 맞춰질 예정이다. 이번 IEDM 2019 행사에서 키옥시아는 플래시 메모리 분야에서 회사가 지속적으로 기울이는 R&D 노력을 반영하는 여섯 편의 논문을 발표했다.